# Analyzing a $\chi$ Model of a Turntable System using Spin, CADP and Uppaal

E. Bortnik <sup>a</sup>, N. Trčka <sup>b</sup>, A.J. Wijs <sup>c,1</sup>, S.P. Luttik <sup>b,c</sup>, J.M. van de Mortel-Fronczak <sup>a</sup>, J.C.M. Baeten <sup>b</sup>, W.J. Fokkink <sup>c,d</sup>, J.E. Rooda <sup>a</sup>

<sup>a</sup>Department of Mechanical Engineering, Eindhoven University of Technology, P.O.Box 513, 5600 MB Eindhoven, The Netherlands

<sup>b</sup>Department of Mathematics and Computer Science, Eindhoven University of Technology, P.O.Box 513, 5600 MB Eindhoven, The Netherlands

<sup>c</sup>Department of Software Engineering, CWI,P.O.Box 94079, 1090 GB Amsterdam, The Netherlands

<sup>d</sup> Vrije Universiteit Amsterdam, Department of Theoretical Computer Science, De Boelelaan 1081a, 1081 HV Amsterdam, The Netherlands

#### **Abstract**

Nowadays, due to increasing system complexity and growing competition and costs, industry makes high demands on powerful techniques used to design and analyze manufacturing systems. One of the most popular techniques to do performance analysis is simulation. However, simulation-based analysis becomes insufficient since it cannot guarantee the correctness of a system. Furthermore, it is not suitable for functional analysis. Our research focuses on examining other methods to do performance analysis and functional analysis, and trying to combine the two. One of the approaches is to translate a simulation model that is used for performance analysis to a model written in an input language of an existing verification tool. We translate a  $\chi$  [1] simulation model of a turntable system into models written in the input languages of the tools CADP [2], SPIN [3] and UPPAAL [4] and do a functional analysis with each of them. This allows us to evaluate the usefulness of these tools for the functional analysis of  $\chi$  models. We compare the input formalisms, the expressiveness of the temporal logics, and the algorithmic techniques for model checking, that are used in those tools.

$<sup>^1</sup>$  Corresponding author. Tel.: +31-20-592-4165; fax: +31-20-592-4199.  $E\text{-}mail\ address:}$  A.J.Wijs@cwi.nl (A.J.Wijs).

## 1 Introduction

The  $\chi$  language is a modeling and simulation language for the specification of industrial systems. It can be used for creating discrete-event, continuous or combined, so-called hybrid, models. The language and simulator have been successfully applied to a large number of industrial cases, such as an integrated circuit manufacturing plant, a brewery and process industry plants [5]. Simulation is a powerful technique for performance analysis, like calculating throughput and cycle time, but for functional analysis (verification) it is less suitable. It can, for instance, show that (a model of) a system has a deadlock but it cannot show that the system is deadlock-free. For the purpose of verification first the discrete-event part of  $\chi$  has been formalized [6]. The language was mapped onto the very expressive, process algebra like, language called  $\chi_{\sigma}$  for which an operational semantics was defined and a state space generator has been built [6]. Recently, a new formalization of  $\chi$ , including the hybrid part, resulted in a more elegant language [7]. The discrete-event part of this language is very similar to  $\chi_{\sigma}$  [8].

The main goal of the TIPSy project [9] (Tools and Techniques for Integrating Performance Analysis and System Verification) is to combine performance analysis with verification, particularly in the  $\chi$  environment. At the start of this project we are focusing on verification. There is no tool support for the new version of  $\chi$  yet and the current toolset for  $\chi_{\sigma}$  is a prototype, meant only for educational purposes. Therefore it is not comparable, when it comes to state space generation, to more developed toolsets. Since we do not expect that a dedicated tool for  $\chi$ , that would be able to compete with existing optimized model checkers, could be built within reasonable time, our aim is to translate  $\chi$  models to input languages of other existing tools. While doing this, we want to compare input formalisms of different tools and see which are best suited for translating  $\chi$  models to. We also want to investigate the expressiveness of temporal logics and algorithmic techniques for model checking that are used in those tools.

For this paper, we choose the well-known specification and verification tools CADP [2], SPIN [3] and UPPAAL [4]. There are several reasons why we make this choice:

- (1) The three tools are quite popular and have been used to detect design errors in applications from many different domains.

- (2) Each tool has a different input language. We use  $\mu$ CRL [10] as the modeling language for CADP. It is an action-based, process algebraic (ACP[11,12,13]) language with excellent data support. Spin's input language, Promela, is a state-based, imperative language. Finally, Uppaal's input language is a specific class of timed automata, combining

- both action-based and state-based features.

- (3) Each tool handles time differently.

- (4) Each tool has a different logic for expressing properties of a model. In CADP, regular alternation-free  $\mu$ -calculus [14] is applied, while SPIN and UPPAAL use a temporal logic, LTL and TCTL [15] respectively.

- (5) Each tool uses a different strategy for verification. In CADP (with  $\mu$ CRL as input) the whole state space must be built. Spin does model checking on-the-fly. Uppaal checks invariant and liveness properties by on-the-fly exploration of the state space of a system in terms of symbolic states represented by constraints.

Our case study is a turntable device, a rotating drilling machine. We choose this particular case study because:

- (1) It is not too complex; otherwise it would take the emphasis away from translating and comparing and make the modeling unnecessarily difficult.

- (2) It is complex enough in the sense that it contains many interesting features to model, such as parallelism and time.

- (3) It is a case study that has been used before [6], making it possible for us to look at existing models and extend them.

- (4) We have access to a physical turntable system and we can use it to perform physical experiments.

In this document, we show how the turntable model can be mapped to the input languages of the mentioned tools and how it can be verified in those environments. We do not cover translations of general  $\chi$  models and rather focus on the turntable only, but it should be clear that the same story holds for a large class of  $\chi$  specifications. Of course, models resulting from a translation of  $\chi$  models might be very different from those made from scratch. Our aim is to have translations resemble the original  $\chi$  model closely so that possible verification errors in these translations can be related back to the original model. We show that many interesting properties of the turntable can be verified but that none of the three tools can easily express all of them. We also compare experiences of working with the tools and results such as the number of states generated.

The structure of the document is as follows: First, the turntable device is explained. Then, we give an introduction to  $\chi$  and present the model of the turntable. The next three sections are devoted to each tool. We give an overview of the input language and the verification mechanism, we explain how we deal with the translation problems and we present the verification of the turntable in detail. The last section gives some comparisons and conclusions.

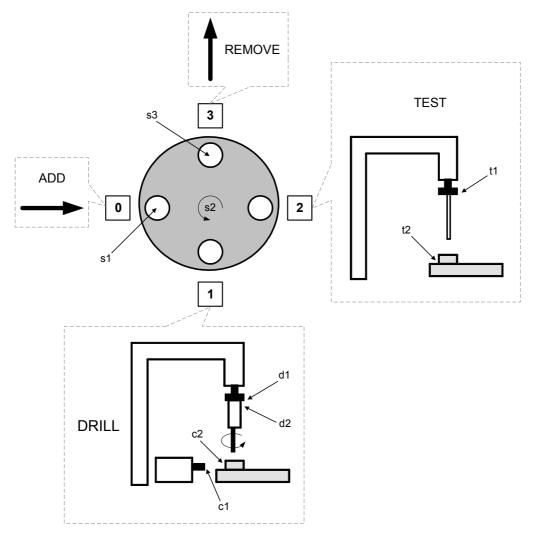

Fig. 1. The turntable system

## 2 Turntable description

The turntable system is an example of a real-life manufacturing system that is used for (real-time) control research [6,16,17].

The turntable system consists of a round turntable, a clamp, a drill and a testing device (Figure 1). The turntable transports products to the drill and the testing device. The drill drills holes in the products. After drilling a hole the products are delivered to the tester, where the depth of the hole is measured, since it is possible that drilling went wrong. To control the turntable system, sensors and actuators are used. A sensor detects a physical phenomenon, and changes its state. The controller reads the state of the sensor, and sends output to actuators. The actuators translate output from the controller to a physical change in the machine.

The turntable has four slots that can hold a product. Each slot can hold at most one product and can be in input, drill, test or output position. There are three sensors attached to the turntable: the sensor s1 at the input position (to detect if a product has been added by the environment), the sensor s3 in the output position (to detect if a product has been removed by the environment) and the sensor s2 that detects whether the turntable has completed the turn.

The drilling module consists of the drill and the clamp. Every product should be locked before drilling and unlocked afterwards. To detect whether the clamp is locked or not two sensors are used (c1 and c2 respectively). The drill also has two sensors to detect whether the drill is in its up (d1) or down (d2) position. These sensors are located above the surface of the turntable, so it is not possible to say whether the product has been drilled successfully or not.

In the testing position there are two sensors to detect whether the tester has reached its up (t1) or down (t2) position. If the tester has reached its down position the test result of the product is good and if the sensor at the down position did not send a signal during a certain amount of time the test result of the product is bad.

The turntable controller system consists of the main controller, turntable controller, drill controller, and tester controller. The main controller supervises the other controllers and the environment. It stores current information about products and operations being performed and based on this information it issues commands to the other controllers and the environment to start operations. When operations are completed the main controller updates the information about the products.

The turntable controller gets signals from the turntable sensors and passes them to the main controller. It also starts rotation of the turntable at the command of the main controller.

The drill controller supervises the drill and the clamp. It switches the drill on/off and commands to lock/unlock the clamp or to start or stop drilling. The drill controller also gets signals from the drill and clamp sensors.

The test controller sends a signal to the tester to start the operation. Then it waits for a signal from the sensor at the down position. If the hole is not deep enough, the sensor is not activated and the current product should be rejected.

The operation-routing sequence of each product is following: add a product to the input position, make a turn (now product is in the drilling position), lock the clamp, switch on the drill, drill, switch off the drill, unlock the clamp, make another turn (now product is in the test position), test, and make a turn again (product is in the removing position).

No product can be added if the adding slot is not empty. No drilling, testing or removing can be performed if the corresponding slot is empty. The turntable can treat up to four products at the same time, that means that the operations can be done in parallel.

**Design rules and assumptions** Creating the model we consider only "good weather" behavior, i.e. the assumption is that the system works without faults and there is no product loss. The initial state is defined as follows: all slots are empty and no operation is started.

For reasons of simplicity, we decided to concentrate on the control system. That means that we do not model material flow as this information can be obtained from the information stored by the main controller.

We assume that the main controller sends messages to the environment to allow adding and removing of products and the environment informs the main controller when the operations are completed. The environment can skip the adding or removing operations. A product can be removed from the removing position only if it has been drilled properly. If a product has a good test result and it has not been removed, it should not be drilled and tested again. If a product has a bad test result it must be drilled and tested again. That means that the information whether product has been added or removed is necessary only after the rotation of the turntable.

When the other sensors change their states, the control system must be notified immediately. For instance, if the clamp sensor does not report that the clamp is locked, the drill cannot start drilling. This difference causes different implementation of the sensors. The turntable sensor states are checked by the control system just before a turn, while the other sensors inform the control system about their state changes immediately.

We also assume that the order of starting and ending of the adding, drilling, testing and removing operations is not known in advance.

The execution of each turntable operation requires a certain amount of time. Because the duration of the turntable operations has not been defined anywhere, we have decided to use the delays, that have been defined in other turntable models, like [6]. We assume that the environment needs 2 time units to perform adding or removing of a product. The clamp needs 2 time units to lock or unlock a product. The drilling operation takes 3 time units and returning the drill to its up position takes 2 time units. Testing and returning the tester to its initial (up) position require 2 time units each.

Verification properties Traditionally, verification properties have been classified into safety and liveness properties. Safety is usually defined as a set of properties that the system may not violate, while liveness is defined as the set of properties that the system must satisfy [3]. Safety, then, defines that something bad will never happen, and liveness defines that eventually something good will happen.

Given those assumptions we want to verify the following properties:

- (1) The system does not contain a deadlock, i.e. it cannot come to a state from which it cannot continue operating (safety).

- (2) If drilling (testing, adding or removing) is started then it is also finished and the turntable doesn't rotate in the meantime (liveness).

- (3) If the product has a bad test result then the product remains on the table and is drilled again (liveness).

- (4) If the product has a good test result then the remover will be called to remove the product (liveness).

- (5) No drilling (testing or removing) takes place if there is no product in the slot and no adding is performed if there is a product in the slot (safety).

- (6) Every added product is drilled in the next rotation (liveness).

- (7) Every product eventually leaves the table (liveness).

- (8) When a product is added it takes between 21 and 30 time units to get its test result (liveness).

The property 7 is a liveness property that requires a *fairness* principle, which makes this property the most complicated one.

First, a product can be removed only if it has a good test result. However, the remover can always decide not to remove and the tester can always generate bad test results. This can happen because the choices whether the product will be removed and whether the test result of the product is good or bad are non-deterministic. In order to verify this property we must put some notion of fairness to the verification process, i.e. exclude unfair paths, in which a product yields a bad test result infinitely often.

Second, since there are at most four products on the table it can happen that one of the products stays on the table while the other ones are drilled properly and removed. In order to verify that every product will eventually be removed we must identify them in some way. The most common solution is to give colors to the products, for instance, red and white, and change the adder so that it adds (non-deterministically) zero or more white products, then one red, and then again zero or more white ones. We want to make sure that if a red product is added then a red one will leave the table eventually. Another solution would be to assign unique identifiers to products or use some other way to distinguish them.

The fairness constraints can be expressed syntactically in linear temporal logic (like PLTL), but not in branching temporal logic (like CTL). In  $\mu$ -calculus fairness properties can be expressed very efficiently [14].

The last property (so-called *bounded liveness*) also requires identification of the products. First we calculate manually the time interval within which a test result of a product is known based on the assumptions. After that we check this interval automatically.

# 3 The turntable model in $\chi$

## 3.1 The $\chi$ language

The  $\chi$  language was designed as a *hybrid*, modeling and *simulation* language. Since we are interested only in discrete-event models and verification, we present here just a part of the language, disregarding features that are used for simulation and to model hybrid behavior. For a complete reference of  $\chi$ , see [1]. The discrete-event subset of  $\chi$  is described in [18].

**Data types** The  $\chi$  language is statically strongly typed. Every variable has a type which defines the allowed operations on that variable. The basic data types are boolean, natural, integer and real numbers and enumerations. The language provides a mechanism to build sets, lists, array tuples, record tuples, dictionaries, functions, and distributions (for stochastic models). Channels also have a type that indicates the type of data that is communicated via the channel.

Time model The time in  $\chi$  is dense, i.e. timing is measured on a continuous time scale. The weak time determinism principle, or sometimes called the time factorization property, (time doesn't make a choice) and maximal progress (a process can delay only if it cannot do anything else) are implicit. The time additivity (if a process can delay first  $t_1$  and then immediately following  $t_2$  time units then it can delay  $t_1 + t_2$  time units from the start) is not present. Delaying is enforced by the delay operator but some processes can also implicitly delay, e.g. send.

Atomic processes The atomic processes of  $\chi$  are process constructors and they cannot be split into smaller processes. They are:

- (1) The assignment process (x := e). It assigns the value (must be defined) of expression e to variable x. It doesn't have the possibility to delay.

- (2) The skip process. It performs the internal action  $\tau$  and cannot delay.

- (3) The send process (m!e). It sends the value of the expression e via channel m. The value of e must be defined and of the right type. It is able to delay arbitrarily long.

- (4) The receive process (m?x). It receives a value via the non-empty channel m and assigns it to the variable x which must be of the right type. It is also able to delay arbitrarily long.

- (5) The delay process  $(\Delta e)$ . It delays a number of time units equal to the value of the expression e or less. The value of e must be a positive real number.

Communication model Communication in  $\chi$  is synchronous, meaning that a *send* and a *receive* action on a same channel cannot happen individually but only together, as a communication action.

**Operators** Atomic processes can be combined by means of the following operators. We present each one of them together with their (informal) semantics.

- (1) The guard operator ( $\rightarrow$ ). A process  $b \rightarrow p$  behaves as p if the value of the boolean expression (guard) b is true, otherwise it deadlocks.

- (2) The alternative composition operator ([]). A process p [] q represents a non-deterministic choice between p and q.

- (3) The sequential composition operator ( ; ). A process p; q behaves as p followed by the process q.

- (4) The repetition operator (\*). A process \*p behaves as p infinitely many times.

- (5) The parallel operator ( $\parallel$ ). A process  $p \parallel q$  executes p and q concurrently in an interleaved fashion, i.e. the actions of p and q are executed in arbitrary order. If one of the processes can execute a *send* action and the other one can execute a *receive* action on the same channel then they communicate, in other words  $p \parallel q$  executes the communication action on this channel.

- (6) The scope operator ( $[[ \ | \ ]]$ ). A process  $[[ \ s \ | \ p \ ]]$  behaves as p in a local state s. The state s is used to define local variables and channels visible only to the process p. It is recursively defined as the empty state or as dcl, s' where s' is a state and dcl is a variable declaration (x : type[=val]) or a channel declaration (m : ?type for receiving and m : !type for sending).

**Process definitions** The language  $\chi$  provides the possibility to define processes. We don't give a syntax definition here but rather an example:

```

\mathsf{proc}\ p(c:?\mathsf{nat}\ ,\ b:\mathsf{bool}\ ) = [\![\ x:\mathsf{nat}\ ]\!]\ b \to c?x[\!]

```

The process p has two arguments, a channel c that can transport natural numbers and a boolean variable b. It has only one local variable, x. The process can now be instantiated (e.g. p(m, y > 7)) inside another process.

#### 3.2 The turntable model

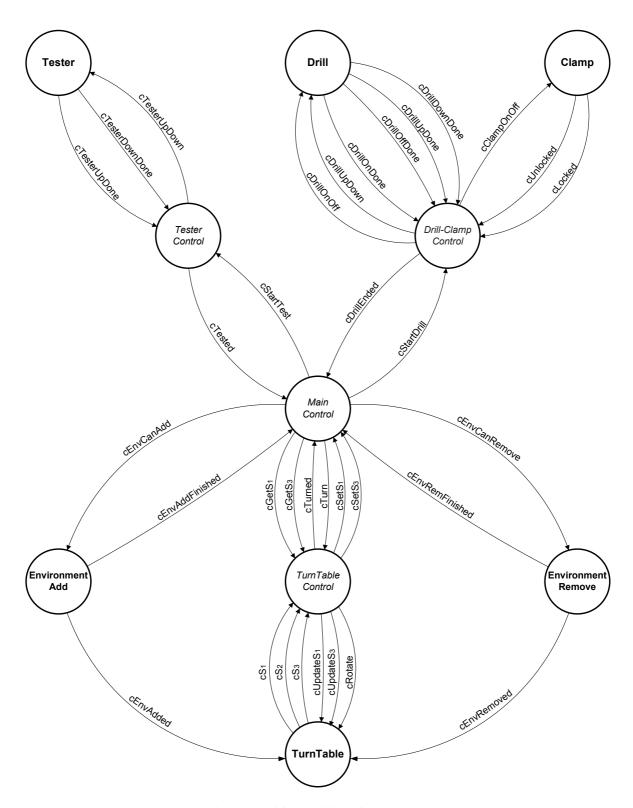

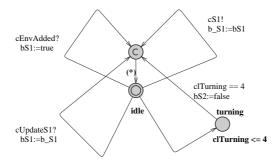

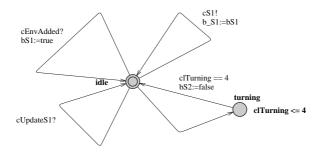

The turntable system architecture is depicted in Figure 2. The mechanical components are represented by means of the processes tester, drill, clamp and turn\_table. These components are controlled by switching commands: cDrillOnOff switches the drill on/off, cDrillUpDown instructs the drill to start or stop drilling, cClampOnOff instructs the clamp to lock or unlock the product, and cTesterUpDown instructs the tester to start or stop testing. The other signals that are used are cRotate (commands the turntable to start turning), cEnvCanAdd, cEnvCanRemove (inform the environment that it can perform adding or removing operations respectively). As already mentioned, the sensors are implemented in several ways (more explanations are given in the descriptions of the corresponding processes).

The control system model consists of the main controller, drill and clamp controller, tester controller and turntable controller which are modeled by means of the processes  $main\_control$ ,  $drill\_control$ ,  $tester\_control$  and TTC respectively. The processes  $env\_add$  and  $env\_remove$  represent the environment.

Below we explain all processes in detail. Of each process, a description is given followed by the  $\chi$  code that models the component.

The turn\_table process In the turn\_table process we define three boolean variables representing the turntable sensors. The variables bS1 and bS3 correspond to the sensors at the adding and removing positions respectively. The variable bS2 corresponds to the turntable sensor that detects whether the turntable is rotating or not. The current states of the sensors are sent via channels cS1, cS2, cS3. The sensor states are updated by the environment when a product is added or removed (cEnvAdded, cEnvRemoved). In the real system the states of these sensors are automatically updated while turning. To achieve this we add two more channels (cUpdateS1, cUpdateS3). A different way to model a change of the sensor states can be found later in the description of the main\_control process. When the turn\_table gets the signal cRotate it performs a delay. Reading and updating the sensors are 'atomic' and instantaneous actions. The control system is modeled in such a way that it is not possible to perform those actions in parallel. This allows us to use alternative composition instead of the parallel one and reduce the state space.

Fig. 2. The turntable model architecture

```

proc Turn\_table(\ cEnvAdded,\ cEnvRemoved\ ,\ cRotate,\ cUpdateS1,\ cUpdateS3:? bool ,\ cS1,\ cS2,\ cS3:! bool )= \parallel bS1: bool = false, bS2: bool = false, bS3: bool = false, x: bool \mid *(\ cS1!bS1\ \mid\ cS2!bS2\ \mid\ cS3!bS3\ \mid\ cEnvAdded?bS1\ \mid\ cEnvRemoved?x;\ bS3:= false \mid\ cUpdateS1?bS1\ \mid\ cUpdateS3?bS3\ \mid\ cRotate?bS2;\ \Delta4.0;\ bS2:= false )

```

The clamp process The clamp has one actuator that is used to switch it on/off (cClampOnOff). The clamp also has two sensors to detect if it is locked or unlocked. When the states of the sensors are changed, the process clamp reports to the control system via the channels cLocked and cUnlocked.

```

\begin{array}{c} \operatorname{proc} \ Clamp(\ cClampOnOff:?\operatorname{bool}\\ \quad , \ cLocked, \ cUnlocked:!\operatorname{bool}\\ )=\\ \|[\ x:\operatorname{bool}\\ |\ *(\ cClampOnOff?\ x;\ \Delta 2.0;\ cLocked!\operatorname{true}\\ \quad ; \ cClampOnOff?\ x;\ \Delta 2.0;\ cUnlocked!\operatorname{true}\\ \quad )\\ \|[\ ]\end{array}

```

The drill process The drill is controlled by two independent actuators. One of the actuators is used to switch the drill on/off (cDrillOnOff). The other one (cDrillUpDown) instructs the drill to start drilling or to return in its initial (up) position. The states of the sensors are detected through the channels cDrillDownDone, cDrillUpDone. The commands are handled independently, that is why we use the parallel composition in the drill process. On the other hand, both actuators are the parts of the one physical component (the drill) and that is why we do not represent them by means of two separate  $\chi$  processes, instead, we combine them into one process.

```

\begin{array}{c} \operatorname{proc} \operatorname{Drill}(\operatorname{cDrillUpDown}, \operatorname{cDrillOnOff}:?\operatorname{bool} \\ \operatorname{,} \operatorname{cDrillUpDone}, \operatorname{cDrillDownDone} \\ \operatorname{,} \operatorname{cDrillOnDone}, \operatorname{cDrillOffDone}:!\operatorname{bool} \\ \operatorname{)=} \\ \|[\operatorname{x}:\operatorname{bool} \\ |*(\operatorname{cDrillUpDown}?\operatorname{x}; \Delta 3.0; \operatorname{cDrillDownDone}!\operatorname{true} \\ \operatorname{;} \operatorname{cDrillUpDown}?\operatorname{x}; \Delta 2.0; \operatorname{cDrillUpDone}!\operatorname{true} \\ \operatorname{)} \\ \|*(\operatorname{cDrillOnOff}?\operatorname{x}; \operatorname{cDrillOnDone}!\operatorname{true} \\ \operatorname{;} \operatorname{cDrillOnOff}?\operatorname{x}; \operatorname{cDrillOffDone}!\operatorname{true} \\ \operatorname{)} \\ \|

```

The tester process The tester is controlled by one actuator (cTesterUp-Down) that is used to start or stop testing. It has two sensors as well. One of them is used to detect a test result of a product. The other one detects whether the tester is in its initial (up) position. Possible test results are implemented by non-deterministic choice. When the test result of a product is good the process tester sends a signal via the channel cTesterDownDone. Otherwise, the process tester waits for the command to move up to the initial position (cTesterUpDown) and, then, sends a signal through the channel cTesterUpDone.

```

\begin{array}{c} \operatorname{proc} \ \operatorname{Tester}(\ \operatorname{cTester} \operatorname{UpDown}: ? \operatorname{bool} \\ \quad , \ \operatorname{cTester} \operatorname{UpDone}, \ \operatorname{cTester} \operatorname{DownDone}: ! \operatorname{bool} \\ ) = \\ \| \ x : \operatorname{bool} \\ | \ \ast ( \ \operatorname{cTester} \operatorname{UpDown} ? \ x \\ \quad ; \ \Delta 2.0 \\ \quad ; \ ( \operatorname{cTester} \operatorname{DownDone} ! \operatorname{true} \ \| \ \operatorname{skip}) \\ \quad ; \ \operatorname{cTester} \operatorname{UpDown} ? \ x \\ \quad ; \ \Delta 2.0 \\ \quad ; \ \operatorname{cTester} \operatorname{UpDone} ! \operatorname{true} \\ ) \\ \| \end{array}

```

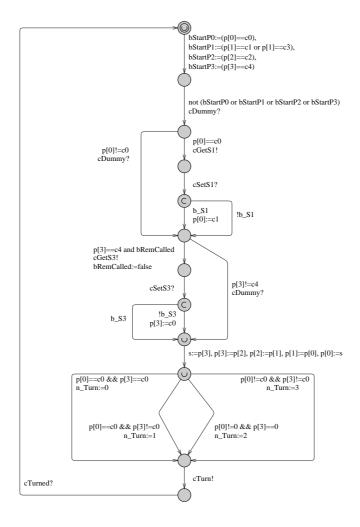

The  $main\_control$  process The  $main\_control$  process keeps track of the slot states and operates the other controllers. We use four integer variables  $(p\theta, p1, p2, p3)$  to describe the state of every slot. The variable values range from 0 to 4 (0 means that there is no product in the slot, 1 - there is a product in the slot and it is not drilled, 2 - a product has been drilled, 3 - a product has been tested and has a bad test result, and 4 - a product has been tested and has a good test result). First, the  $main\_control$  process checks the states of the slots and starts corresponding processes (adding, drilling, testing

and removing). As we assumed, the order of starting and finishing of these operations can vary and is not known a priori. In order to implement it, we use nested parallelism. The operations (cEnvCanAdd, cStartDrill, cStartTest, cEnvCanRemove) are started according to the following rules:

- The environment is allowed to add a product if there is no product in the slot.

- Drilling can be performed if there is a product in the slot and it has not been drilled yet or it has a bad test result.

- Testing is allowed if there is a product in the slot and it has been drilled.

- The environment is allowed to remove a product if there is a product in the slot and it has a good test result.

If these operations have been started the main\_control process waits till they are completed (cEnvAddFinished, cEnvRemFinished, cTested, cDrillEnded). After that, it gives the command to the turntable controller (the process TTC) to read the states of the sensors at the adding and removing positions (cGetS1, cGetS3) and gets their current states (cSetS1, cSetS3). If their states have been changed (that means that the products have been added or removed), the main\_control updates the information about current slot states. Then, it sends the command to the turntable controller to rotate the turntable (cTurn) and waits till the turn is completed (cTurned). Then, the loop is repeated. In the real system the states of the sensors at adding and removing positions are automatically updated during the turn. To achieve this in the model we send new states of the turntable sensors over the channel cTurn. In our model main\_control sends the value of the sensors after the turn over the channel cTurn (the information is coded as an integer in following way: p = 0 means that there is no product in the adding and removing positions, p=1 means that there is no product in the adding position and there is a product in the removing slot, p=2 means that there is a product in the adding position and there is not product in the removing position, p=3 means that there are products in both slots). Another approach to update the sensor states is to duplicate the information about all slots in the turn\_table process [6]. This approach allows one to separate the physical and control systems easier and simpler but leads to a larger state space.

```

proc Main_control( cDrillEnded, cTested, cTurned, cSetS1

, cSetS3:? bool

, cEnvCanAdd, cEnvAddFinished

, cStartDrill, cStartTest

, cEnvCanRemove, cEnvRemFinished

, cGetS1, cGetS3:!bool, cTurn:!nat

[x, y : bool, p : nat = 0, pp : nat = 0,

p0: nat = 0, \ p1: nat = 0, \ p2: nat = 0, \ p3: nat = 0

| *( (

( p\theta = 0 \rightarrow cEnvCanAdd! true; cEnvAddFinished?x

p\theta \neq 0 \rightarrow \text{skip}

\parallel ( p1 = 1 \lor p1 = 3 \rightarrow cStartDrill! true; <math>cDrillEnded?x; p1 := 2

\parallel ( p2 = 2 \rightarrow cStartTest! true; cTested?y; (y \rightarrow p2 := 4 \parallel \neg y \rightarrow p2 := 3)

p2 \neq 2 \rightarrow \text{skip}

\parallel ( p3 = 4 \rightarrow cEnvCanRemove!true; cEnvRemFinished? x

p3 \neq 4 \rightarrow \text{skip}

; ( p\theta = 0 \rightarrow cGetS1! true; cSetS1? x

; (x \to p\theta := 1 \parallel \neg x \to \text{skip})

\parallel p\theta \neq 0 \rightarrow \text{skip}

; ( p3 = 4 \rightarrow cGetS3! true; cSetS3? x; (\neg x \rightarrow p3 := 0 \parallel x \rightarrow skip)

[] p3 \neq 4 \rightarrow \text{skip}

p_{1}:=p_{2}; p_{3}:=p_{2}; p_{3}:=p_{3}; p_{3}:=p_{3}:=p_{3}; p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=p_{3}:=

p : (p0 = 0 \rightarrow (p3 = 0 \rightarrow p := 0) | p3 \neq 0 \rightarrow p := 1)

\| p0 \neq 0 \rightarrow (p3 = 0 \rightarrow p := 2 \| p3 \neq 0 \rightarrow p := 3)

; cTurn!p; cTurned?x

)

```

The  $drill\_control$  process The process  $drill\_control$  gets the command to start drilling from the  $main\_control$  over the channel cStartDrill. Then, it sends a signal to lock the clamp (cClampOnOff) and waits for the reply from the clamp sensor (cLocked). When the clamp is locked the  $drill\_control$  uses the other switching command (cDrillOnOff) to start drilling and waits for the confirmation (cDrillOnDone). Then, it gives a signal to start drilling (cDrillUpDown), waits for confirmation from the sensor (cDrillDownDone), sends a signal to return the drill in its initial (up) position (cDrillUpDown), and waits for

confirmation from the sensor (cDrillUpDone). Then, the  $drill\_control$  switches the drill off (cDrillOnOff), and waits for confirmation (cDrillOffDone). After that, the  $drill\_control$  switches the clamp on again (cClampOnOff), waits for the signal from the clamp sensor (cUnlocked) and reports to the  $main\_control$  that drilling is completed (cDrillEnded).

```

proc Drill_control( cStartDrill, cLocked, cUnlocked

, cDrillUpDone, cDrillDownDone

, cDrillOnDone, cDrillOffDone

, cDrillEnded : ? bool

, cClampOnOff, cDrillUpDown

, cDrillOnOff :!bool

)=

\| x : \mathsf{bool} \|

|*(cStartDrill?x)|

; cClampOnOff!true; cLocked?x

; cDrillOnOff!true; cDrillOnDone?x

; cDrillUpDown!true; cDrillDownDone?x

; cDrillUpDown!true; cDrillUpDone?x

; cDrillOnOff!true; cDrillOffDone?x

; cClampOnOff! true; cUnlocked? x

; cDrillEnded! true

```

The tester\_control process Tester\_control gets a command to perform testing from main\_control (cStartTest) and switches tester on (cTesterUp-Down). To perform the testing operation, tester needs 2 time units. If the tester has reached its down position within 2 time units, the test result of the product is good (cTesterDownDone) and if the sensor does not react in 2 time units, the test result of the product is bad. However, in our model tester\_control waits for the signal from the tester for 4 time units instead of 2. The reason for this is that if tester and tester\_control delay for the same amount of time, there is a possibility that tester\_control would make its choice before tester. So, in order to ensure that tester always makes its choice before tester\_control the latter delays longer. In that case, tester makes a choice in 2 time units and after that tester\_control has no choice anymore. Then, tester\_control stores the test result (bTstRes), switches tester off (cTesterUpDown), and sends the test result to main\_control over the channel cTested.

```

\begin{array}{c} \operatorname{proc} \ Tester\_control(\ cStartTest,\ cTesterDownDone \\ ,\ cTesterUpDone:?\operatorname{bool} \\ ,\ cTesterUpDown,\ cTested:!\operatorname{bool} \\ )=\\ \|[\ x,\ bTstRes:\operatorname{bool} \\ |\ *(\ cStartTest?\ x \\ ;\ cTesterUpDown!\operatorname{true} \\ ;\ (cTesterDownDone?\ bTstRes \\ \|\ \Delta 4.0;\ bTstRes:=\operatorname{false} \\ )\\ ;\ cTesterUpDown!\operatorname{true} \\ ;\ cTesterUpDone?\ x \\ ;\ cTested!\ bTstRes \\ )\\ \ \end{array}

```

The TTC process The process TTC (the turntable controller) gets commands from  $main\_control$  to perform the turn or update sensor information. When the turn is completed TTC sends a signal to  $main\ control$  over the channel cTurned.

```

proc TTC(\ cTurn: ?nat,\ cS1,\ cS2,\ cS3

,\ cGetS1,\ cGetS3: ?bool

,\ cSetS1,\ cSetS3,\ cUpdateS1,\ cUpdateS3

,\ cRotate,\ cTurned: !bool

)=

[[\ x:bool,\ bS1:bool=false,\ ss:nat=0]

|*(\ cTurn?ss;\ cRotate!true

;\ cUpdateS1!ss=2\lor ss=3

;\ cUpdateS1!ss=1\lor ss=3

;\ cS2?x;\ cTurned!true

[\ cGetS1?x;\ cS1?bS1;\ cSetS1!bS1

[\ cGetS3?x;\ cS3?bS3;\ cSetS3!bS3]

)

```

The environment processes There are two environment processes in the model: adding and removing. They get appropriate signals from  $main\_control$  to add or remove a product (cEnvCanAdd, cEnvCanRemove). After performing (or skipping) the operations the environment processes notify  $main\_control$  that they have finished (cEnvAddFinished, cEnvRemFinished). If a product is added or removed the environment processes send corresponding messages to the  $turn\_table$  process through the channels (cEnvAdded, cEnvRemoved).

```

proc \ Env\_add(\ cEnvCanAdd:?\ bool\ ,\ cEnvAdded \\ ,\ cEnvAddFinished:!\ bool\ )= \\ \|[\ x:\ bool\ ] *(\ cEnvCanAdd?\ x \\ ;\ (skip\ \|\ cEnvAdded!\ true) \\ ;\ cEnvAddFinished!\ true \\ ) \\ \| proc\ Env\_remove(\ cEnvCanRemove:?\ bool\ ,\ cEnvRemoved \\  \  \  ,\ cEnvRemFinished:!\ bool\ )= \\ \|[\ x:\ bool\ ] *(\ cEnvCanRemove?\ x \\  \  ;\ (cEnvRemoved!\ true\ \|\ skip) \\  \  ;\ cEnvRemFinished!\ true \\ ) \\ \|

```

The state space As already mentioned, there is no tool available for  $\chi$  yet. Therefore we have generated the state space in the  $\chi_{\sigma}$  toolset with the following results: the number of states is 32570 (6839 states after minimization under strong bisimulation).

# 4 Promela/Spin

# 4.1 Introduction to Promela/Spin

The full presentation of PROMELA, a very complex language, is beyond the scope of this paper. We give here only a brief overview mentioning only those parts of the language that we are interested in. For more information, see [3,19,20] or consult the SPIN's web page http://spinroot.com.

PROMELA's syntax is derived from C [21], with communication primitives from CSP [22] and control flow statements based on the guarded command language [23]. It has many language constructs similar to  $\chi_{\sigma}$  constructs.

A common specification consists of global channel declarations, variable declarations and process declarations with possibly one special init process. Process declarations specify behavior, channel and variable declarations define the environment in which the processes run. Prometa has a rather limited set of

data types, only bool, byte, short, int (all with the unsigned possibility) and channels. It also provides a way to build records and arrays and to define macros (processed by the C language preprocessor). Message channels are declared, for instance, as chan m = [2] of {int} meaning that the channel is buffered and it can store (at most) two values of type integer (has only one field of type int). Channels can also be of length 0, i.e. unbuffered, to model synchronous communication. They can also have more than one field, not necessarily of the same type.

Every variable must be declared before use. The exception is the special dummy variable '\_' which is a predefined write-only variable, that can be used to store scratch values. The type of this global variable is int. It is an error to use or reference its value.

Process declarations are of this form:

```

proctype name(parameters) {

local variables and channels;

body

}

```

Local variables and channels specify the local state of the process and they are not visible to other processes. The same rules as for global variables apply here. The body is a list of statements, itself a statement. Any expression can be used as a statement, enabled precisely if it evaluates to a non-zero value. Assignments are also statements and have the usual semantics. The skip statement executes the action (1) and has no effect on variables. The send statement (m!e\_1,...,e\_n) sends a tuple of values of the expressions e\_i to the channel m. The receive statement (m?E\_1,...,E\_n) retrieves a message from the non-empty channel m, for every E\_i that is a variable assigns a value of e\_i to it and for every other E\_j makes sure that its value matches the value of the e\_j. If the channel is buffered, a send is enabled if the buffer is not full; a receive is enabled if the buffer is non-empty. On an unbuffered channel, a send (receive) is enabled only if there is a corresponding receive (send) that can be executed simultaneously. There are also many variants of these statements (message can be left in or removed from a channel after receiving, send/receive can only be offered etc.)

There are several ways to combine statements. The alternative composition is defined by the selection statement:

```

if

:: statements

...

:: statements

```

fi.

It selects one among its options and executes it. An option can be selected if its first statement is executable. A selection blocks until there is at least one selectable option. If more than one option is selectable, one will be chosen non-deterministically. The repetition is achieved by the statement

do

:: statements

...

:: statements

od.

It is similar to the selection statement except that the choices are executed repeatedly, until control is explicitly transferred to outside the statement by break or the goto statement. The break terminates the innermost repetition statement in which it is executed and cannot be used outside a repetition.

Another way to combine statements is to use sequential composition denoted as p;q or b -> p. The latter is usually used to emphasize that a process p is guarded by the conditional expression/statement b.

The original version of PROMELA/SPIN is untimed but there is a discrete time extension, called DTPROMELA/DTSPIN [24]. The idea is to divide time into slices and then frame actions into these slices. The time between actions is measured in ticks of a global digital clock. By having a variable t declared as timer, setting its value to some expression that evaluates to a natural number (by doing set(t,e)) and waiting for t to expire (by stating expire(t)) a process can be enforced to postpone its execution for n time slices (where n is the value of e). When DTSPIN executes the timeout action, all timers synchronize and time progresses to a next slice. This action is executed only if no other actions can be executed, meaning that maximal progress is implicit. Deadlock is recognized when timeout is about to happen and all timers are off (not set or already expired).

PROMELA provides two constructs, atomic{stmt\_1;...;stmt\_n} and d\_step{stmt\_1;...;stmt\_n} that can be used to model indivisible events and to reduce a state space. Their purpose is to forbid the statements from inside to interleave with other statements in the specifications. The difference is that additionally d\_step executes all statements as one (one state in the state space). These constructs are very useful but have a limitation: statements other than the first may not block and the d\_step cannot contain send/receive statements on unbuffered channels.

Once declared every process can be started by the PROMELA process creation mechanism, the run statement. The special init process, if present, is

automatically instantiated once, and is often used to prepare the true initial state of a system by initializing variables and running the appropriate process-instances. Processes can be started with different parameters. Once started they execute in parallel with the interleaving semantics. This is the only way to achieve parallelism because there is no explicit parallel operator. Processes communicate with each other through global variables and channels.

#### 4.2 The turntable model in Promela

Translation of  $\chi$  constructs like assignments, skip statement, sequential and alternative composition and repetition is straight-forward since they have obvious equivalents in Promela.

The data types used in the turntable model are also present in PROMELA.

Both languages have a notion of channels. Communication in  $\chi$  is synchronous and consequently all channels in the PROMELA translation are of length zero. For example, channel *cRotate* is declared as chan cRotate = [0] of {bool}.

In general **proc** definitions of  $\chi$  are translated to **proctype** definitions of PROMELA and **init** process is used to run them all.

For example, the *drill\_control* process is translated as

```

do

control() {

do

control() {

control() {

do

control() {

cont

```

Since in the  $drill\_control$  process we use channels only for synchronization, after receiving we don't need the value of x so we replace it by the dummy variable  $_{-}$ . The additional parameter ',1' in cStartDrill? $_{-}$ ,1 will be explained later.

We now present features of which translation requires a more careful consideration.

**Guards** Statements of type  $b \to p$ , in general cannot be just translated as b -> p. This is due to the fact that, since in Promela operator -> is equivalent to the sequential operator and the boolean expression b is also a statement, if the value of b is true, Spin will execute the action (1) (e.g. it will pass the guard) even though process p cannot execute anything. This is different from  $\chi$  which looks for both b to be true and for p to be executable before taking the step.

However, if p in  $b \to p$  is an atomic process there is a way to translate. The guarded assignment such as  $b \to x := e$  is translated as  $\mathtt{d\_step}\{\mathtt{b}; \ \mathtt{x} = \mathtt{e}\}$ . With the  $\mathtt{d\_step}$  operator we force the statement to be executed as one action like in  $\chi$ . If the value of  $\mathtt{b}$  is  $\mathtt{false}$  the statement is blocked and if it is  $\mathtt{true}$ , since an assignment is always executable, the statement will execute only one action. Translation is similar for a guarded skip.

In order to translate guarded send/receive actions we must apply a different trick because those actions can block and therefore cannot be put inside the d\_step statement. For a channel that has send/receive actions involved in guarded statements we first change the declaration by adding another field argument to it, one of an integer type. We need the extra argument to synchronize on guards and we translate  $b \to m!e$  to m!e,b and  $B \to m?x$  to m?x,eval(2-B). We use 2-B instead of just B because the communication between a guarded send and a guarded receive should not take place if both guards evaluate to false (2-B = b is equivalent to B=1 and b=1). The eval function is used to force the evaluation of the expression 2-B. SPIN does not do this automatically in receive statements because the expression can be a variable in which case it should not serve as a match but instead it would be assigned the incoming value from the message field. If a communication action, for example m?x, is not used in the guarded context but its counterpart send is, then it should be translated to m?x,1. This goes similarly for m!e when a corresponding receive is guarded. For example, in the main\_control process a send action on the channel cStartDrill is guarded,  $p_1 = 1 \lor p_1 = 3 \to cStartDrill!true$ , and this statement is translated as cStartDrill!1,(p1 == 1 || p1 == 3). The corresponding receive action, cStartDrill?x in the drill\_control process, is not guarded and therefore translated as cStartDrill?\_,1.

In case of the  $main\_control$  process not only atomic processes are guarded, but also, for example, we see

$$p_0 = 0 \to (p_3 = 0 \to p := 0 \ [] \ p_3 \neq 0 \to p := 1)$$

$[] \ p_0 \neq 0 \to (p_3 = 0 \to p := 2 \ [] \ p_3 \neq 0 \to p := 3)$

To translate this fragment we use the fact that  $b_1 \to (b_2 \to p)$  is equivalent to  $(b_1 \land b_2) \to p$  and that  $b \to (p \parallel q)$  is equivalent to  $(b \to p) \parallel (b \to q)$ . This

assures that we can distribute guards over the operators and have the equivalent process with guarded atomic processes only. The PROMELA translation is therefore:

```

if

:: d_step{(p0 == 0 && p3 == 0) -> p = 0}

:: d_step{(p0 == 0 && p3 != 0) -> p = 1}

:: d_step{(p0 != 0 && p3 == 0) -> p = 2}

:: d_step{(p0 != 0 && p3 != 0) -> p = 3}

fi;

```

Time Note that in the turntable model all the delays are natural numbers so we don't think that much is lost when switching from continuous to discrete time. The  $\Delta n$  statement is translated to the DTPROMELA statement expire(t), where t is timer, previously set to the value of n. In cases where  $\Delta n$  is not involved in a choice, set(t,n) can be present immediately before the expire(t). This is, indeed, the case in the translations of the clamp,  $turn\_table$ , drill, tester,  $env\_add$  and the  $end\_remove$  process. However, in the tester\\_control process there is an alternative composition of delaying and receiving:

```

cTesterUpDown ! true;

( cTesterDownDone ?;

bTstRes := true

[] \Delta 2;

bTstRes := false

);

cTesterUpDown ! true

```

In order to prevent time from making a choice, the set(t,4) must be moved to some place 'safe', i.e. outside of the alternative composition. That is because it is always executable and therefore always available as a choice, while expire(t) is a boolean expression/statement that is blocked until 4 time slices later. The discussed fragment of the tester\_control process is translated as:

```

proctype tester_control(){

bool bTstRes;

timer t;

do

:: cStartTest?_,1; set(t,4);

cTesterUpDown!1;

if

:: cTesterDownDone?_; bTstRes = 1

:: expire(t); bTstRes = 0

```

```

fi;

....

od

}

```

**Parallel operator** In Promela there is no explicit parallel operator. Since processes *drill* and *main\_control* contain it, we encounter a problem when trying to translate them.

In the drill process no variables are shared (except the dummy x that is removed in the PROMELA translation anyway) and the parallel operator is not used in the context of other operators. This means that drill can be split into two smaller processes that can be translated separately:

```

proctype drill1() {

proctype drill2() {

timer t;

dο

do

:: cDrillOnOff?_;

:: cDrillUpDown?_;

cDrillOnDone!1;

set(t,3); expire(t);

cDrillOnOff?_;

cDrillOffDone!1

cDrillDownDone!1;

cDrillUpDown?_;

od

set(t,2); expire(t);

}

cDrillUpDone!1

od

}

```

The drill1 and drill2 are executing in parallel when started in the init process.

On the other hand, in the *main\_control* process, the parallel operator is used within a repetition and a sequential composition context. To solve this problem we use PROMELA's process creation mechanism. The parts of the *main\_control* process that run in parallel are translated to separate process definitions, namely MC1(), MC2(), MC3() and MC4(). These processes should not be started in the init process since they are not available from the beginning. The part that comes after the parallel composition (together with the loop) is also translated to the new process but with the additional statement at the beginning of the loop whose role is to start the new processes. This process is called main\_control and it must be started in the init process.

There is one more problem to solve. After the main\_control process starts its

subprocesses it should be waiting for them to finish, not run in parallel with them as would be the case now. Therefore, some synchronization is needed. We use a global variable WAIT of type integer, initially 0, which is incremented at the end of each subprocess, and for which the main\_control waits to be equal to 4, the number of subprocesses it started. Then, it sets the variable back to 0 (for later use) and continues. Therefore, main\_control is translated as:

Note that since variables  $p_0, p_1, p_2$  and  $p_3$  are shared between parts that are now separate processes in PROMELA, they must be declared in the global scope.

**Remark:** Since parts of the  $main\_control$  process that run in parallel don't communicate with each other the parallel operator here is just an interleaving operator. In some cases the interleaving of actions in PROMELA could also be achieved with one loop and few additional guards (boolean variables). The idea is to associate one guard to each action. If there is a choice between two actions they share the same guard. Only actions available from the start have there guards initially set to true. When an action is executed, its guard is put to false and the guard of the action that comes next is assigned true. This is done in a loop that is exited when all the guards are false. To illustrate the technique we give an example. The interleaving between a; b and c;  $(d \parallel e)$  can be expressed as:

```

bool b1,b2,b3,b4;

d_step{ b1=1; b2=0; b3=1; b4=0; }

do

:: d_step{ b1->a; b1=0; b2=1 }

:: d_step{ b2->b; b2=0 }

:: d_step{ b3->c; b3=0; b4=1 }

```

```

:: d_step{ b4->d; b4=0 }

:: d_step{ b4->e; b4=0 }

:: !(b1 || b2 || b3 || b4) -> break

od;

```

The d\_step is used to prevent state space from growing when introducing extra actions.

However, this approach results in a PROMELA model that is not very similar to the original  $\chi$  model so we use it only to compare the state spaces generated by the  $\chi_{\sigma}$  toolset and SPIN.

# 4.3 Verification of the model in Spin

In this section we first compare state spaces generated by SPIN and  $\chi_{\sigma}$  and later show how we verified the properties of the turntable.

By performing an exhaustive search, SPIN's verifier, almost instantly, reported 100995 states, 188724 transitions and 5.8975MB of memory used (3.342MB for states). To compare this result to the size of the state space generated by  $\chi_{\sigma}$  (32570 states) we switch off all the optimizations of SPIN: like partial order reduction, statement merging and state vector compression. Now the number of states increases to 157576, the number of transitions to 455580. This shows the importance of the optimization features.

The huge difference in the number of states generated by  $\chi_{\sigma}$  and SPIN is mostly the result of the set actions and the statements used for process creation and synchronizing in the  $main\_control$  process. To show this we first force set actions to be executed atomically with the action before. Since this action is always send or receive we can't use the d\_step, only the atomic statement. For example, in the turn\_table process

```

cRotate?bS2; set(t,4);expire(t)

is changed to

atomic{

cRotate?bS2;

set(t,4)

}; expire(t).

```

Similarly in other processes. The number of states drops to 119616 and the number of transitions to 212876. Note that the fact that delays are always one (special) action in  $\chi$  but can be more (timeout) actions in PROMELA and the fact that we used atomic instead of d\_step, also introduce 'extra' states but

this is unavoidable.

Second, instead of using the process creation mechanism we use the other trick (see the remark on page 25) to achieve nested parallelism. This results in 48252 states with 114048 transitions (32768/59154 fully optimized), much closer to the  $\chi_{\sigma}$ 's result. In this case, 9.236MB (7.170MB for states) is needed; 3.132MB (1.026MB for states) when fully optimized.

There are several ways to perform verification of properties in SPIN but we use only LTL formulae verification and trace-assertions. The LTL mechanism checks properties expressed as linear temporal logic formulas over the values of variables (state based). The trace-assertion mechanism assures that the behavior of the system matches the behavior expressed as a deterministic automaton (trace) with only send/receive actions on globally declared channels as labels. In a case where communication is synchronous to prevent SPIN from checking the send offers together with regular sending we use only receive actions as labels.

Now we discuss how the eight properties from section 2.1 can be expressed in a way SPIN understands them:

- (1) The system does not contain a deadlock. Absence of deadlock is verified in SPIN by performing an exhaustive search for invalid end states.

- (2) If drilling (testing, adding or removing) is started then it is also finished and the turntable doesn't rotate in the meantime. To verify this property we introduce two new variables into the PROMELA model, drilling and rotating, both initially 0. The idea is to keep track of states in which the table is turning and the states in which the drilling is going on. We set the drilling to 1 when the master controller sends a message to the drill controller instructing it to start drilling (d\_step{cStartDrill!1; drilling = 1}), and set it back to 0 when master controller is informed that the drilling is finished (d\_step{cDrillEnded!1; drilling = 0}). We do a similar thing for rotating. The d\_step is used to prevent the state space from growing after the additional statement is added.

The property is now expressed as the LTL formula

[](drilling == 1 -> (rotating == 0 U drilling == 0))

Similarly, for testing, adding and removing.

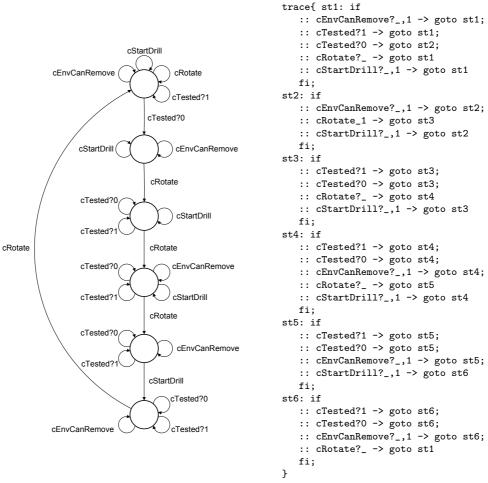

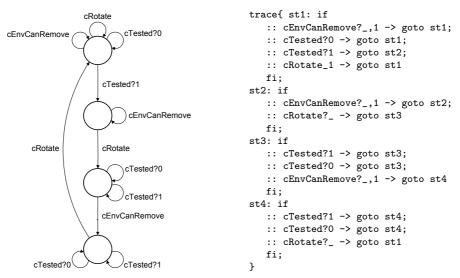

(3) If the product has a bad test result the product remains on the table and is drilled again (when it comes to the drilling position). Since the result of testing is communicated through the channel cTested and since it is easy to express the number of rotations we find the trace-assertion mechanism more suitable to verify this property then LTL. We must first rephrase this property so that it can be expressed with receive actions only: if a bad test result is received then in the next

rotation the master controller doesn't instruct the remover to remove and in the next two rotations (when we are back to the drilling position) the driller will drill the product again. Now we state this behavior as:

(4) If the product has a good test result the remover will be called to remove the product. Similarly to the previous case we can rephrase the property and come out with the following trace:

(5) No drilling (testing or removing) takes place if there is no product in the slot and no adding can be performed if there is a product in the slot). The LTL formula that represents this property is:

but the following event-trace can be used as well:

and similarly for other cases.

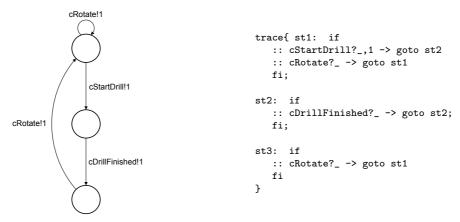

(6) Every added product is drilled in the next rotation. This property can be interpreted as: when you add and rotate afterwards then you must drill before you rotate again. The corresponding automata is:

```

trace{ s1: if

:: cEnvAdded_1; goto s2;

cStartDrill

cRotate

:: cRotate_1; goto s1;

:: cStartDrill?_,1; goto s1;

cEnvAdded

cStartDrill

:: cRotate_1; goto s3;

:: cStartDrill?_,1; goto s2;

fi;

cRotate

cRotate

:: cEnvAdded 1: goto s3:

cEnvAdded

:: cStartDrill?_,1; goto s4;

fi:

cStartDrill

s4: if

:: cEnvAdded_1; goto s4;

:: cRotate_1; goto s1;

cEnvAdded

```

(7) Every product eventually leaves the table. To verify this property we first introduce a variable pstn that can have values 0, 1, 2 and 3. It represents the position of the turntable (or some mark on the rotating disk) with respect to the adding position. After every rotation the value of pstn is changed by the rule pstn = (pstn + 1) % 4. Second, variables removed and added are introduced. They keep track in which position the product was removed (added). They have two extra values:

-1, meaning that the removing (adding) was skipped, and -2, a neutral value. The variable removed (added) is set to the neutral value after the remover (adder) has made a choice, to remove (add) or to skip. To verify the property we must now prove the following four LTL formulas:

```

[](added == 0 -> <> removed == 3)

[](added == 1 -> <> removed == 0)

[](added == 2 -> <> removed == 1)

[](added == 3 -> <> removed == 2)

```

We are sure that we are removing the same product we are adding since added cannot become 0 twice if removed doesn't become 3 in between (in the first formula, similarly for the other three). That is because if the product is not removed in 4k + 3 rotations then in the next rotation we don't add because there is already a product in the slot. To add fairness we forbid the remover to always skip removing while in the position 3 (with a product to remove in place) and to always generate bad test results in the position 2 (with a product to test in place). The extended formula is:

```

(

[](pstn==3 && p3==4 -> <> removed == 3) &&

[](pstn==2 && p2==2 -> <> (bTstRes == 1 && pstn == 2)

) -> [](added == 0 -> <> removed == 3)

```

(8) When a product is added it takes between 21 and 30 time units to get its test result. For this property we must calculate the number of clock ticks (timeout actions) between adding a product and receiving its test result. To achieve this we must keep track of timeout's somehow. Since they are not communication actions, trace assertion mechanism is ruled out. To use LTL mechanism we may try to add a special timer that counts ticks (it decreases accordingly) but because DTSPIN does not allow values of timers in LTL formulas this would not be of much help. Another solution is to use timeout in formulas or to code the property directly as a never claim but at this moment it is hard to see how this can be done in an optimal and satisfactory way.

We here present a solution that is based on the fact that, if the product is added in some position that no product is added in the same position before the test result is known. Because we have to distinguish products again, we use the same idea (variable pstn) as before. Here we check that if adding happens in the position 0 then result is known in position 2 in 21-30 time units. Similarly for other positions.

We introduce a variable, called added0, which becomes 0 when adding does not happen (already a product in the slot) or is skipped (in the position 0), and 1 when product is added (in the position 0). When added0 becomes 1, we also set a special timer variable, called TT, to 30. The idea is to check if TT has a value less or equal to 9(=30-21) in a place where test result is obtained (in the position 2) and adding has previously happened (in the position 0). This is done by assertion mechanism of Spin, directly in code:

```

cTesterUpDone?_;

if

:: (added0 == 1 && pstn == 2) -> assert(TT.val < 10)

:: else

fi;

cTested!bTstRes;</pre>

```

# $5 \mu CRL/CADP$

# 5.1 The language $\mu CRL$

Basically,  $\mu$ CRL is based on the process algebra ACP [11], extended with equational abstract data types [25]. In order to intertwine processes with data, actions and recursion variables can be parametrized with data types. More-

over, a conditional construct (if-then-else) can be used to have data elements influence the course of a process, and *alternative quantification* (also called *choice quantification*) is added to sum over possibly infinite data domains.

The language comes with a toolset [26] that can build a state space from a specification and store it in the .aut format, one of the input formats of the model checker CADP [2] (more on this model checker in paragraph 5.3). Next to that, in order to strive for precision in proofs, an important research area is to use theorem provers such as PVS [27] to help in finding and checking derivations in  $\mu$ CRL. A large number of distributed systems have been verified in  $\mu$ CRL, often with the help of a proof checker or theorem prover [28,29].

We will give a short overview of the language. For a complete reference, see [10].

**Data types** Initially there are no data types known in a  $\mu$ CRL specification. Therefore each specification should start by defining the necessary data types and the functions that work on them. In fact, it is mandatory to define the boolean type in each specification, since the conditional construct works with boolean expressions. In the case of the turntable model, the natural numbers were also defined. One can virtually define any data type.

In  $\mu$ CRL one can specify abstract data types [25] in an algebraic way, with an explicit recognition of so-called *constructor* function symbols, which intuitively cannot be eliminated from data terms [10]. In the case of natural numbers the zero (0) and the successor function S are constructors, while addition (plus) is not. For booleans we have the constructors true (T) and false (F). This explicit recognition of constructor symbols makes it possible to enumerate the elements of a data type.

To define a data type one uses the keyword **sort**. A sort represents a non-empty set of data elements. To declare the sort of booleans one can write:

sort Bool

Now the elements of the data type can be declared. This is done with the keywords func and map. A constructor symbol, declared with func, has as target the data type in question. For the booleans we declare T and F both with func:

$\begin{array}{ll} \texttt{sort} & \texttt{Bool} \\ \\ \texttt{func} & \texttt{T,F:} {\rightarrow} \texttt{Bool} \\ \end{array}$

What we state here is that the elements of Bool are T and F.

Now that the structure of the data type is given, one can add additional

functions. These can be defined with map. For the booleans we define the function and and the equality relation eq.

Using rewrite rules one can now define how the functions work. When defining, it's allowed to use variables, which have to be defined first using var. Having added the rewrite rules for and and eq, the declaration of Bool now looks like this:

```

sort

Bool

T,F: \rightarrow Bool

func

eq:Bool#Bool→Bool

map

and:Bool#Bool→Bool

var

x,y:Bool

eq(x,x) = T

rew

eq(T,F) = F

eq(F,T) = F

and(T,x) = x

and(x,T) = x

and(F,x) = F

and(x,F) = F

```

In a similar way one can define the sort of natural numbers with the equality relation eq and the addition function plus:

```

sort

Nat

func 0:\rightarrow Nat

S:Nat \rightarrow Nat

plus:Nat\#Nat \rightarrow Nat

map

eq:Nat#Nat→Bool

x,y:Nat

var

plus(x,0) = x

rew

plus(x,S(y)) = S(plus(x,y))

eq(x,x) = T

eq(0,S(x)) = F

eq(S(x),0) = F

eq(S(x),S(y)) = eq(x,y)

```

Actions In  $\mu$ CRL one can declare actions in the act section of a specification. These actions may have zero, one or several data parameters. When parameters are used the data types of these parameters need to be given. In the next example an action a is defined without a parameter, an action b is defined with a parameter of type Bool and an action c is defined with two parameters of type Nat and Bool respectively:

act a

b:Bool

c:Nat#Bool

One can allow processes P and  $\mathbb{Q}$  to communicate in the parallel process  $P \parallel \mathbb{Q}$ . To do this it is possible to define which actions are able to synchronize with each other using the keyword comm. The following example states that the actions d and e can synchronize and form the action f together:

comm d | e = f

Finally the process deadlock  $(\delta)$ , which cannot terminate successfully, and the internal action  $\tau$  are predefined.

**Operators** There are eight operators in  $\mu$ CRL. We present each one of them with an informal semantics.

- (1) The alternative composition operator (+). A process p+q proceeds (non-deterministically) as p or q (if they can proceed).

- (2) The sum operator  $(\sum_{d:D} X(d))$ , with X(d) a mapping from the data type D to processes, behaves as  $X(d_1) + X(d_2) + \ldots$ , i.e., as the possibly infinite choice between X(d) for any data term d taken from D. This operator is used to describe a process that is reading some input over a data type [30].

- (3) The sequential composition operator (.). A process p.q proceeds as p followed by q.

- (4) The process expression  $p \triangleleft b \triangleright q$  where p and q are processes, and b is a data term of data type Bool, behaves as p if b is equal to T (true) and behaves as q if b is equal to F (false). This operator is called the conditional operator, and operates as a then\_if\_else construct.

- (5) The parallel operator ( || ). A process p || q executes p and q concurrently in an interleaved fashion, i.e. the actions of p and q are executed in arbitrary order. For all actions a and b which can communicate with each other: If one process can execute a and the other one can execute b then p and q can communicate (p || q executes the communication action).

- (6) The encapsulation operator  $(\partial_{\mathtt{H}})$ . A process  $\partial_{\mathtt{H}}(\mathtt{p})$  disables all actions of

- p that occur in the set  $H \subseteq Act$ . Typically this operator is used to enforce that certain actions synchronize.

- (7) The renaming operator  $(\rho_f)$ , with  $f: Act \to Act$ , is suited for reusing a given specification with different action names. The subscript f signifies that the action a must be renamed to f(a). The process  $\rho_f(p)$  behaves as p with its action names renamed according to f.

- (8) The abstraction operator  $(\tau_{\mathtt{I}})$ . A process  $\tau_{\mathtt{I}}(\mathtt{p})$  'hides' (renames to  $\tau$ ) all actions of  $\mathtt{p}$  that occur in the set  $\mathtt{I} \subseteq \mathtt{Act}$ .

**Process definitions** The heart of a  $\mu$ CRL specification is the proc section, where the behavior of the system is declared. This section consists of recursion equations of the following form, for  $n \ge 0$ :

proc

$$X(x_1:s_1, \ldots, x_n:s_n) = t$$

Here X is the process name, the  $x_i$  are variables, not clashing with the name of a function symbol of arity zero nor with a parameterless process or action name, and the  $s_i$  are sort names, expressing that the data parameters  $x_i$  are of type  $s_i$ . Moreover, t is a process term possibly containing occurrences of expressions  $Y(d_1, \ldots, d_m)$ , where Y is a process name and the  $d_i$  are data terms that may contain occurrences of the variables  $x_1, \ldots, x_n$ . In this rule,  $X(x_1, \ldots, x_n)$  is declared to have the same (potential) behavior as the process expression t [10].

The initial state of the specification is declared in a separate initial declaration init section, which is of the form

init

$$X(d_1, \ldots, d_n)$$

Here  $(d_1, \ldots, d_n)$  represents the initial behavior of the system that is being described. In general, in  $\mu$ CRL specifications the init section is used to instantiate the data parameters of a process declaration, meaning that the  $d_i$  are data terms that do not contain variables. The init section may be omitted, in which case the initial behavior of the system is left unspecified.

The time model Delaying for a certain amount of time is impossible in  $\mu$ CRL at first glance. This is because  $\mu$ CRL does not work with time. A later extension of  $\mu$ CRL to timed  $\mu$ CRL [31] introduced the notion of time. However, at present creating a timed  $\mu$ CRL specification is not very practical since the  $\mu$ CRL toolset can only parse timed  $\mu$ CRL code and cannot generate a state space from it.

There is another way however to simulate some notion of discrete time. In

this paper we use a method based on the one from [32]. In short it works like this: first we define two actions: tick and tick2. The tick action represents the end of a time slice and the beginning of a new one. In order to share this notion of time all running processes need to synchronize their tick actions. If at least one of these processes is busy and therefore unable to perform a tick the tick action will not take place. This synchronization aspect is essential if one wants to use global timing. Note that, using this technique, we get discrete time in  $\mu$ CRL, since we represent a time period as a number of time units.

In most cases when using time in a model the modeler would like to give normal actions priority over tick actions. In order to realize this  $\chi$  has implicit maximal progress, but in  $\mu$ CRL an operator for this does not exist. We can however get similar results by using the tick2 action and post-processing the system after linearization (more on the latter in section 5.2).

The differences between tick2 and tick are the following:

- The action tick is used for translating delays, while tick2 is used to make an action delay-able (which means adding a tick2 self-loop as an alternative to this action);

- A tick action can synchronize with any number of tick or tick2 actions, but a tick2 action cannot synchronize with only tick2 actions (at least one tick action is needed for going from one time unit to the next).

Now, several delay-able processes can delay together if there is a tick action enabled in at least one process.

## 5.2 The turntable model in $\mu CRL$

In the next few paragraphs we will look at the  $\mu$ CRL model of the turntable which resulted from translating the original  $\chi$  model. The  $\mu$ CRL language will be explained as far as needed. Translating the turntable model was done in an intuitive fashion in order to get some inspiration for developing a translation scheme for translating  $\chi$  specifications to  $\mu$ CRL specifications. In this paper therefore the way in which we ended up with this  $\mu$ CRL model will not be discussed in detail. We restrict ourselves to highlighting the interesting parts. Translating  $\chi$  constructs like an assignment, a *skip* statement, a sequential composition and a guard can be translated straightforwardly since there exist similar constructs in  $\mu$ CRL. Here we have to note that except for translating the atomic processes all other translations involve the usage of a program counter n. This counter is used to control the order of execution within a process. Initially, when a process starts its execution, the counter equals zero. By changing the value each time an action is executed and including the counter in the guards accompanying the actions one can specify the order in

which these actions should be executed. Since we translated  $\chi$  processes to Linear Process Equations (LPEs) we needed such a counter to translate (for instance) sequential compositions. Later in this section a definition of LPE can be found. How the program counter functions in practice will become apparent when looking at the translations in the next few paragraphs.

Following are remarks on the constructions that could not be translated in an obvious way:

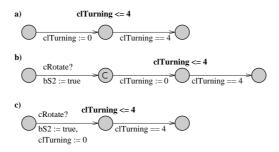

- In the  $\mu$ CRL model we move from one time slice to the next by synchronizing tick actions of all the processes in the system. This means that we use discrete timing. Delays in  $\chi$  should therefore always be 'discretizable'. A  $\chi$  delay of n time units is then translated to n tick actions placed in sequence.

- The usage of time in combination with communication actions is tricky when translating. If you have a send action in one process and a corresponding receive action in another which (if any) of the actions can be delayed until the other action can be executed? In principle both send and receive actions are delay-able in  $\chi$ . The maximal progress operator then ensures that possible communications get a higher execution priority than a delay. In other words: Both send and receive actions can delay if communication is not possible. Once communication is possible it will be executed immediately.

In  $\mu$ CRL however, making all send and receive actions delay-able may result in communications being delay-able as well, since we cannot assign different priorities to actions (see the time model paragraph in section 5.1); there is no maximal progress operator. Communications that turn out to be delay-able in the  $\mu$ CRL specification are therefore bad translations. These can be fixed once the specification is linearized using the  $\mu$ CRL toolset though: The linearized version can be (automatically) manipulated in such a way that these communications become non-delay-able again. In short, to do this the guards of all tick actions have to be changed in such a manner, that tick actions only become enabled if no 'normal' (non-tick) action is.

- Another problem is translating an alternative composition: How to translate it depends on the number of alternatives that begin with a delay or are delay-able. This is due to the weak time determinism principle [18]: The passage of time cannot result in making a choice between the alternatives that can perform the time transition. In other words: Can both alternatives perform a delay, then they can delay together after which a choice can still be made. This principle led basically to two different possible translations of an alternative composition when translating the turntable model: